# FABRICATION AND INTEGRATION OF ONE- AND TWO-DIMENSIONAL MATERIALS FOR ADVANCED NANOSCALE DEVICES

### Aidar Kemelbay

A thesis is submitted in partial fulfillment of the requirement of Nazarbayev University for the degree of Doctor of Philosophy

### Supervisory committee:

Dr. Alexander Tikhonov, Nazarbayev University

Dr. Marat Kaikanov, Nazarbayev University

Dr. Tevye Kuykendall, Lawrence Berkeley National Laboratory

### **Abstract**

As the miniaturization of electronic circuits reach physical limits, new materials and physical phenomenon need to be exploited to further increase device density and efficiency. A number of approaches have been proposed. One of the common approaches in the scientific community is the search to understand and practically fabricate novel materials and devices at the nanoscale. In this work, we present several nanofabrication processes and unique synthetic methods that we have developed to achieve novel 1D and 2D semiconducting, dielectric, and ferroelectric materials, relevant for the integration in advanced nanoscale devices.

In particular, **single-walled carbon nanotubes** (CNTs) were synthesized and integrated into bottom- and top-gate field effect transistors. We demonstrated a novel CNT surface pretreatment method that enables uniform and conformal ALD coating of suspended nanotubes with various dielectric materials. Obtained all-oxide  $TiO_2$ - $Al_2O_3$  compound high- $\kappa$  dielectric showed an improved dielectric permittivity.

Another class of semiconductor that we investigated, was **transition metal dichalcogenide** (TMD) layered thin film materials. We developed a novel synthetic method that we termed "lateral conversion," which was used to grow WS<sub>2</sub>, WSe<sub>2</sub>, MoS<sub>2</sub> and MoSe<sub>2</sub> van der Waals materials. In this method, a metal-oxide layer is converted into TMD material using a chalcogenation reaction that propagates laterally between two inert silica layers. The method results in a multilayer structure with TMD material covered by a capping layer that protects it from the environment, contamination, and oxidation. It was shown that the technique provides control over the TMD position, shape, and thickness with sub-micron precision, at wafer scale.

A third class of materials that was studied in this work are hafnia-based ferroelectric thin films. The ability to integrate ferroelectric thin films into

electronic devices with atomic layer deposition (ALD) has been a long-standing dream. With the discovery of ferroelectric properties in ALD hafnium oxide, the realization of some advanced architecture devices became one step closer. Here, ALD was used to synthesize  $Hf_{0.5}Zr_{0.5}O_2$ , with precisely tuned stoichiometry. Next, the crystallization of initially amorphous  $Hf_{0.5}Zr_{0.5}O_2$  was performed using widely researched rapid thermal annealing (RTA), as well as by using intense pulsed ion beams (IPIBs), which was done for the first time for such application. RTA-produced ferroelectric thin films, showed successful orthorhombic phase stabilization and annealing-temperature-dependent remnant polarization, whereas early IPIBs experiments demonstrated the ability to crystallize  $HfO_2$ ,  $ZrO_2$  and  $Hf_{0.5}Zr_{0.5}O_2$  thin films, inducing different crystallographic phases.

### Acknowledgements

This thesis is lovingly dedicated to my mother, Roza Kabenovna Mussenova. Without her none of my achievements would have been possible.

First of all, I would like to thank my supervisors – Dr. Tevye Kuykendal, Dr. Alexander Tikhonov and Dr. Marat Kaikanov. Dr. Tevye Kuykendal for hosting, teaching and guiding me in Berkeley for five years. Dr. Alexander Tikhonov for giving me the opportunity to work in his group and endless support in every aspect of my research and PhD life. Dr. Marat Kaikanov for introducing me to a fascinating world of accelerators. I express special appreciation to Dr. Shaul Aloni (Molecular Foundry) for his help with designing experiments and sample characterization, as well as for all the useful discussions.

I am truly grateful to the Director of the Nanofabrication Facility (Molecular Foundry) Dr. Stefano Cabrini for his support and the opportunity to work in a world-class research center. I also thank Dr. Adam Schwartzberg for his valuable insights on ALD and other fabrication techniques. It was a great pleasure to work with the Nanofabrication Facility staff, especially with Michael Elowson and Arian Gashi, from whom I learned a lot and who continuously make sure that every cleanroom user can perform high-quality research. I want to thank the Director of the Inorganic Facility (Molecular Foundry) Dr. Jeff Urban for giving me an opportunity to start my project at the Molecular Foundry. I am also grateful to Inorganic Facility staff, especially to Tracy Mattox for her help with XPS measurements and training.

My extended thanks go to Zaure táte for her love and care. I also thank my friends – Alkey Margulanuly, Arman Tuigynbek, Omar-Sayan Karabayev and Yernar Smagulov. I would particularly like to commend Arman, who supported me throughout these years. Last but not least, I am grateful to my relatives – Kozhakhmetov, Ospanov, Sabitov, Kenzheguzinov and Aliyev families.

Financial support from the Nazarbayev University (small grant 090118FD5346) and the Ministry of Education and Science of the Republic of Kazakhstan (state-targeted program BR05236454) are acknowledged. Work at the Molecular Foundry was supported by the Office of Science, Office of Basic Energy Sciences, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

### **Declaration**

I declare that the research contained in this thesis, unless otherwise formally indicated within the text, is the original work of the author. The thesis has not been previously submitted to this or any other university for a degree and does not incorporate any material already submitted for a degree.

Aidar Kemelbay February 22nd, 2020

# **Contents**

| Al | ostrac  | et                                        |                                                              | i    |

|----|---------|-------------------------------------------|--------------------------------------------------------------|------|

| A  | cknov   | vledgem                                   | nents                                                        | iii  |

| De | eclara  | tion                                      |                                                              | v    |

| Li | st of A | Abbrevi                                   | iations                                                      | viii |

| Li | st of l | Figures                                   |                                                              | X    |

| Li | st of [ | <b>Fables</b>                             |                                                              | xi   |

| No | meno    | clature                                   |                                                              | xii  |

| 1  | Intr    | oductio                                   | n                                                            | 1    |

| 2  | Stat    | e-of-the                                  | e-art                                                        | 4    |

|    | 2.1     | Conve                                     | entional FETs and scaling theory                             | 4    |

|    | 2.2     |                                           | low power switches                                           | 6    |

|    | 2.3     | d 2D nanomaterials for future electronics | 8                                                            |      |

|    |         | 2.3.1                                     | Carbon nanotubes                                             | 9    |

|    |         | 2.3.2                                     | Transition metal dichalcogenides                             | 17   |

|    | 2.4     | Ferroe                                    | electricity and negative capacitance                         | 20   |

|    |         | 2.4.1                                     | Negative capacitance                                         | 21   |

|    |         | 2.4.2                                     | Ferroelectric material structural considerations             | 24   |

|    |         | 2.4.3                                     | Ferroelectric HfO <sub>2</sub>                               | 25   |

|    | 2.5     | Experi                                    | imentally demonstrated negative capacitance                  | 32   |

| 3  | Eng     | ineering                                  | g and integration of high-κ dielectrics into Carbon Nanotube | ;    |

|    | FET     | S                                         |                                                              | 37   |

|    | 3.1     | Single                                    | -walled carbon nanotube synthesis and integration into FETs. | 37   |

|    | 3.2                         | Electrode integration and suspended CNT fabrication                  | 42  |  |  |  |

|----|-----------------------------|----------------------------------------------------------------------|-----|--|--|--|

|    | 3.3                         | ALD thin film integration                                            | 46  |  |  |  |

|    | 3.4                         | Titania-alumina all-oxide high- $\kappa$ dielectric                  | 51  |  |  |  |

| 4  | Lith                        | ographically defined synthesis of transition metal dichalcogenides   | 56  |  |  |  |

|    | 4.1                         | Wafer-scale WS <sub>2</sub> synthesis                                | 56  |  |  |  |

|    | 4.2                         | High-resolution Raman spectroscopy of WS <sub>2</sub>                | 60  |  |  |  |

|    | 4.3                         | Structural characterization of buried WS <sub>2</sub>                | 62  |  |  |  |

|    | 4.4                         | Lateral conversion kinetics                                          | 64  |  |  |  |

|    | 4.5                         | Extensibility of the lateral conversion technique                    | 66  |  |  |  |

| 5  | Syn                         | thesis and characterization of ferroelectric hafnium zirconium oxide | 70  |  |  |  |

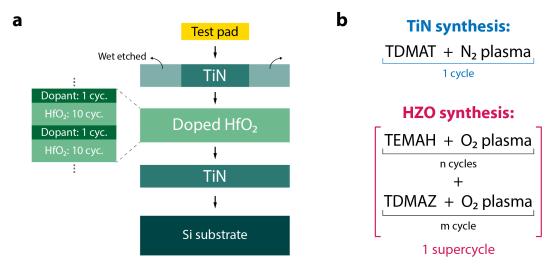

|    | 5.1                         | Metal-insulator-metal stack fabrication                              | 71  |  |  |  |

|    | 5.2                         | Ferroelectricity stabilization in HZO using RTA                      | 75  |  |  |  |

|    | 5.3                         | HZO crystallization using Intense Pulsed Ion Beams                   | 81  |  |  |  |

|    |                             | 5.3.1 IPIB basics and application in materials science               | 81  |  |  |  |

|    |                             | 5.3.2 Interaction volume of proton beam generated on the INURA       |     |  |  |  |

|    |                             | accelerator                                                          | 83  |  |  |  |

|    |                             | 5.3.3 Hafnia and zirconia crystallization using proton beam          |     |  |  |  |

|    |                             | irradiation                                                          | 84  |  |  |  |

| 6  | Con                         | clusions and Outlook                                                 | 90  |  |  |  |

|    | 6.1                         | Summary and conclusions                                              | 90  |  |  |  |

|    | 6.2                         | Outlook                                                              | 92  |  |  |  |

| Bi | bliog                       | raphy                                                                | 94  |  |  |  |

| Αį | ppend                       | lix A. Nanofabrication process flows                                 | 111 |  |  |  |

|    | <b>A</b> 1                  | Carbon nanotube field effect transistor fabrication                  | 111 |  |  |  |

|    | A2                          | Transition metal dichalcogenides synthesis                           | 113 |  |  |  |

|    | A3                          | Ferroelectric hafnium zirconium oxide fabrication                    | 114 |  |  |  |

| Aį | pend                        | lix B. IPIB irradiation parameters                                   | 115 |  |  |  |

| Pu | Publications and projects 1 |                                                                      |     |  |  |  |

| Cı | Curriculum vitae 1          |                                                                      |     |  |  |  |

### **List of Abbreviations**

AFM Atomic Force Microscopy

ALD Atomic Layer Deposition

BOE Buffered Oxide Etch

CMOS Complementary Metal-Oxide-Semiconductor

CNFET Carbon Nanotube Field Effect Transistor

CNT Carbon Nanotube

CPD Critical Point Drying

CVD Chemical Vapor Deposition

ELC Extent of Lateral Conversion

EOT Equivalent Oxide Thickness

FET Field Effect Transistor

FIB Focused Ion Beam

GAA Gate-All-Around

GIXRD Grazing Incidence X-Ray Diffraction

HRTEM High Resolution Transmission Electron Microscopy

HZO Hafnium-Zirconium Oxide

IC Integrated Circuit

IPIB Intense Pulsed Ion Beam

ITRS International Technology Roadmap for Semiconductors

MFM Metal-Ferroelectric-Metal

MIM Metal-Insulator-Metal

MOS Metal-Oxide-Semiconductor

MOSFET Metal Oxide Field Effect Transistor

NA Numerical Aperture

NC Negative Capacitance

O-Phase Orthorhombic Phase

PEALD Plasma Enhanced Atomic Layer Deposition

PECVD Plasma Enhanced Chemical Vapor Deposition

PVD Physical Vapor Deposition

RPM Revolutions Per Minute

RTA Rapid Thermal Annealing

SEM Scanning Electron Microscopy

SS Subthreshold Swing

SWCNT Single-Walled Carbon Nanotube

TEM Transmission Electron Microscopy

TMD Transition Metal Dichalcogenide

WLRM White Light Reflection Microscopy

XPS X-Ray Photoemission Spectroscopy

XRD X-Ray Diffraction

XRR X-Ray Reflectivity

# **List of Figures**

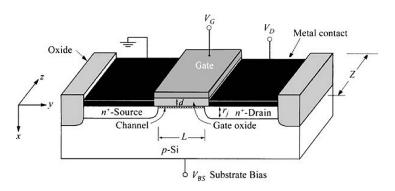

| 2.1 | Schematic illustration of MOSFET                                          | 5  |

|-----|---------------------------------------------------------------------------|----|

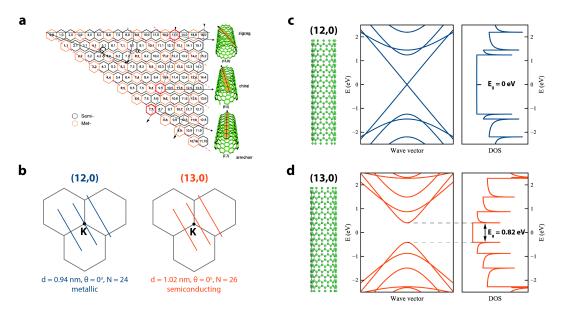

| 2.2 | Chirality-dependent properties of carbon nanotubes                        | 11 |

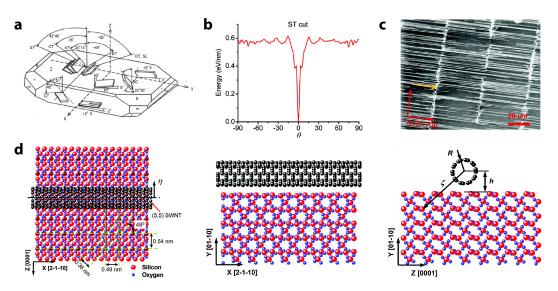

| 2.3 | Graphoepitaxial growth of carbon nanotubes on the surface of quartz       | 14 |

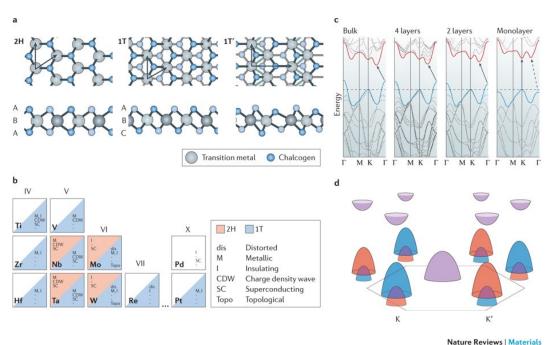

| 2.4 | Transition metal dichalcogenides structure and electronic properties      | 18 |

| 2.5 | Comparison between negative, positive and ferroelectric capacitors .      | 22 |

| 2.6 | Ferroelectricity and structural requirements for it                       | 23 |

| 2.7 | Hafnium oxide polymorphs                                                  | 26 |

| 2.8 | Ferroelectric window of HfO2 and its dependence on fabrication            |    |

|     | conditions                                                                | 27 |

| 2.9 | Ferroelectric characterization of HfO <sub>2</sub> capacitors             | 30 |

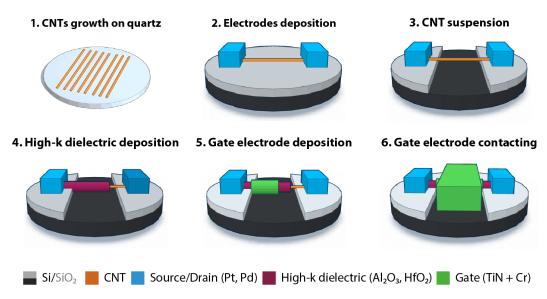

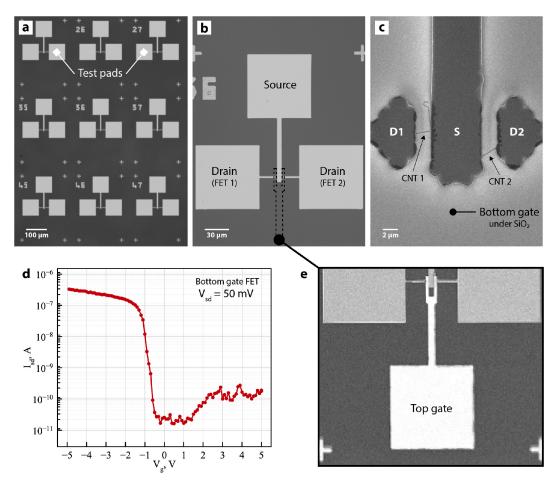

| 3.1 | CNFET fabrication process flow                                            | 38 |

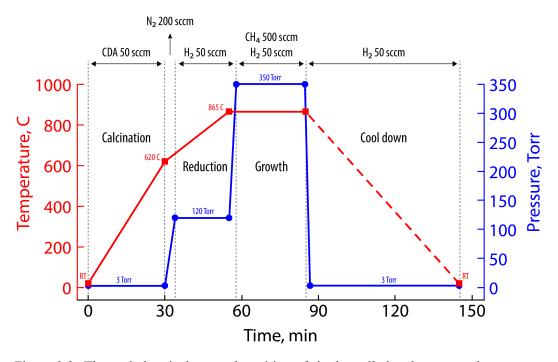

| 3.2 | Thermal chemical vapor deposition of single-walled carbon                 |    |

|     | nanotubes process diagram                                                 | 40 |

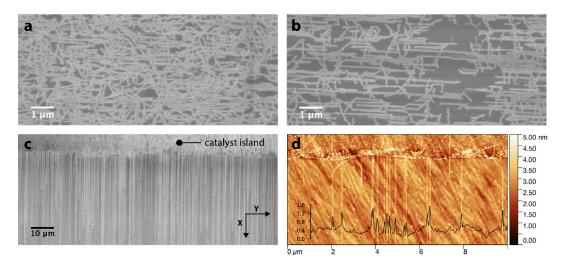

| 3.3 | Graphoepitaxial CNTs on the surface of ST-cut quartz                      | 42 |

| 3.4 | SEM images of lithographically defined electrodes                         | 43 |

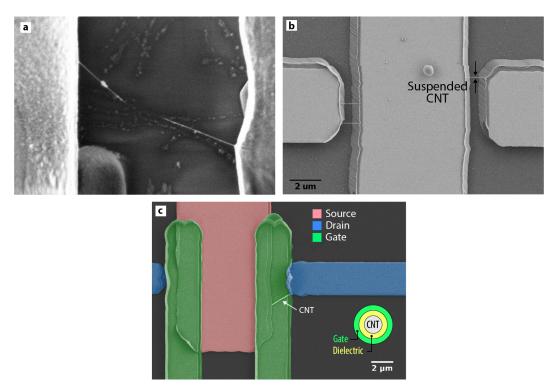

| 3.5 | Suspended carbon nanotube fabrication                                     | 45 |

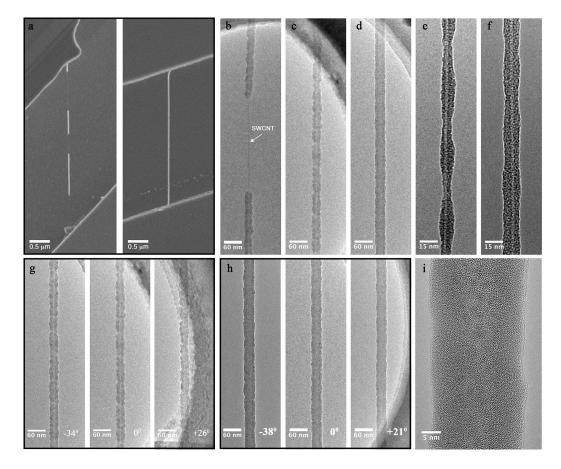

| 3.6 | Morphology of thin films deposited on suspended SWCNTs                    | 49 |

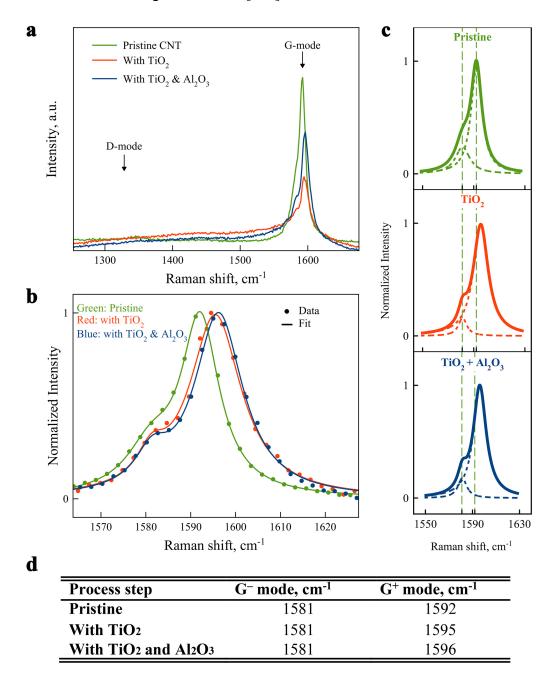

| 3.7 | Raman spectroscopy of a pristine nanotube and a nanotube coated           |    |

|     | with $TiO_2$ and $Al_2O_3$                                                | 51 |

| 3.8 | Chemical composition and dielectric properties of TiO <sub>2</sub> -based |    |

|     | compound dielectric                                                       | 52 |

| 3.9 | Electron transport properties of CNFETs                                   | 54 |

| 4.1 | Lithographically defined WS <sub>2</sub> grown using lateral conversion   |    |

|     | technique                                                                 | 59 |

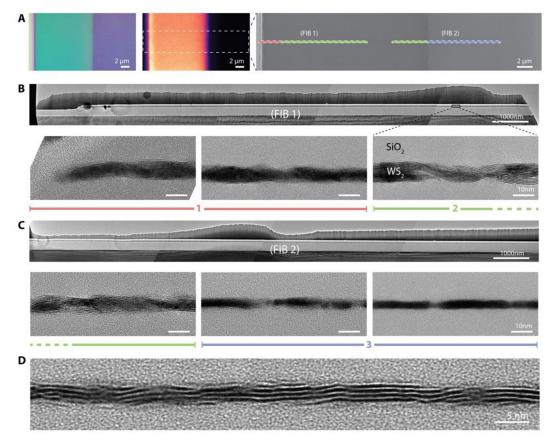

| 4.2 | High-resolution Raman spectroscopy of $WS_2$                              | 61 |

| 4.3 | Structural characterization of WS <sub>2</sub> synthesized using lateral  |    |

|     | conversion                                                                | 63 |

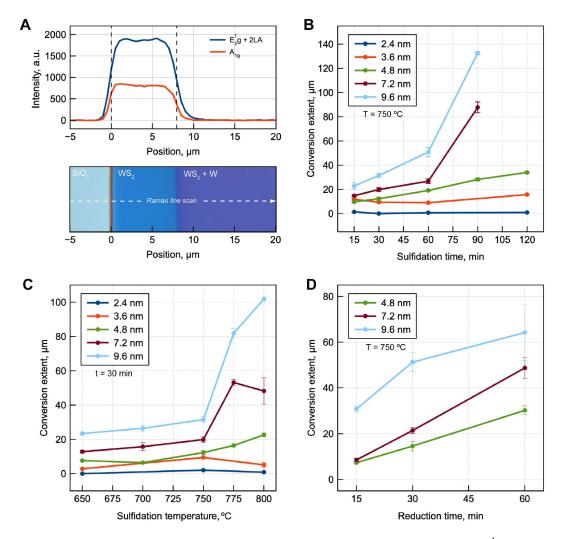

| 4.4 | Lateral conversion kinetics                                                | 65 |

|-----|----------------------------------------------------------------------------|----|

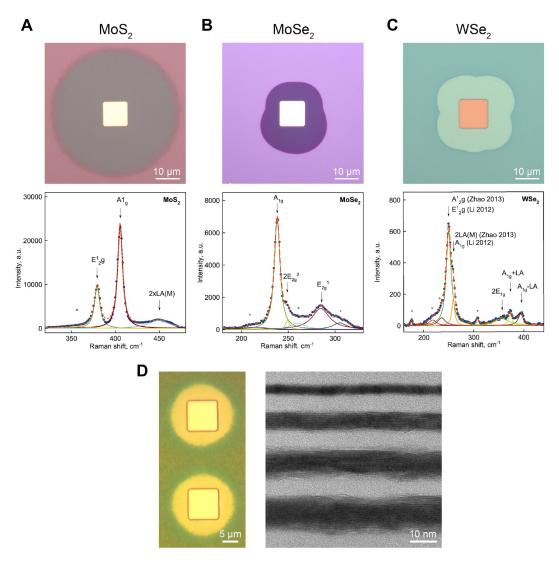

| 4.5 | The extensibility of the lateral conversion technique                      | 68 |

| 5.1 | Metal Insulator Metal capacitor geometry                                   | 71 |

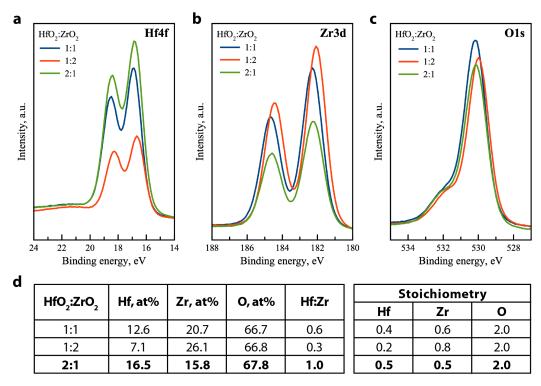

| 5.2 | XPS measurements1 of HZO samples with different HfO2-to-ZrO2               |    |

|     | ALD cycles ratio                                                           | 73 |

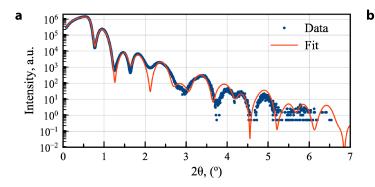

| 5.3 | X-ray reflectivity from a TiN/Hf $_{0.5}Zr_{0.5}O_2$ /TiN multilayer stack | 75 |

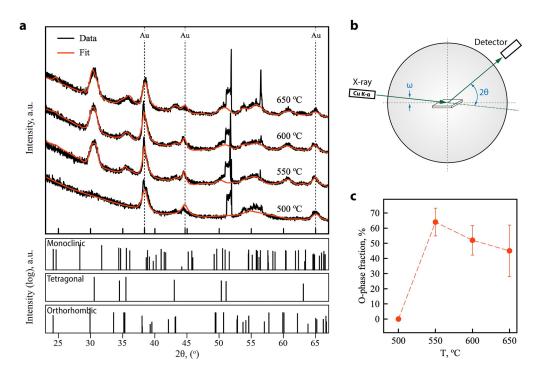

| 5.4 | GIXRD measurement of annealed HZO                                          | 77 |

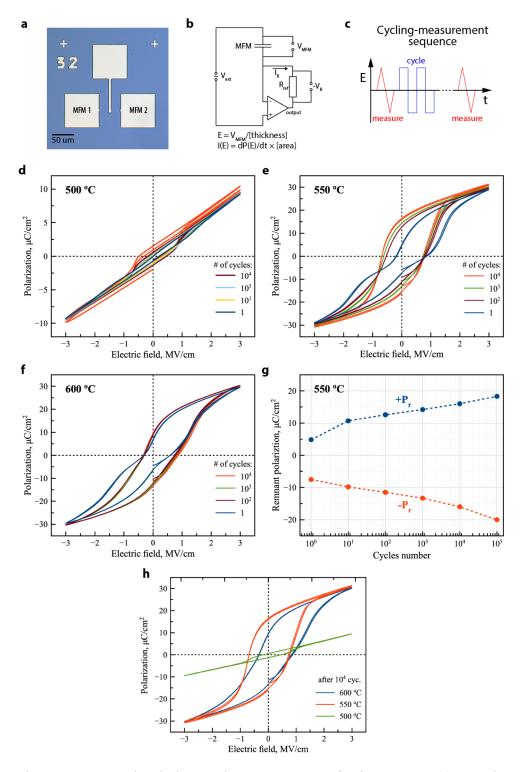

| 5.5 | Ferroelectric hysteresis measurements of $Hf_{0.5}Zr_{0.5}O_2$             | 80 |

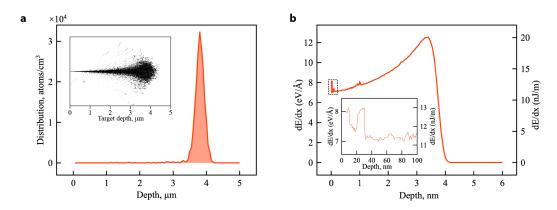

| 5.6 | SRIM simulations of protons traveling inside HfO <sub>2</sub> /Si target   | 84 |

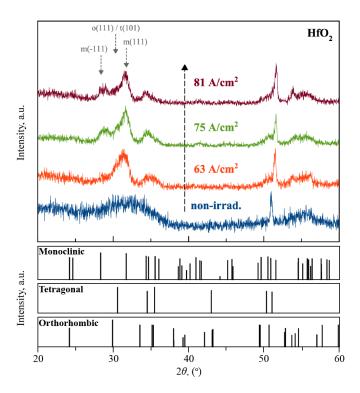

| 5.7 | GIXRD measurements showing crystallization of HfO2 after                   |    |

|     | irradiation with IPIB                                                      | 86 |

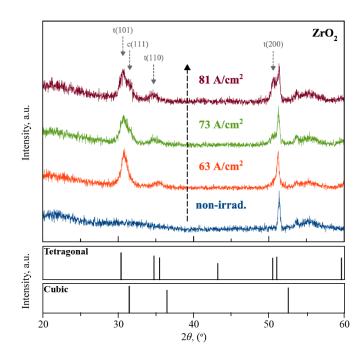

| 5.8 | GIXRD measurements showing crystallization of ZrO2 after                   |    |

|     | irradiation with IPIB                                                      | 87 |

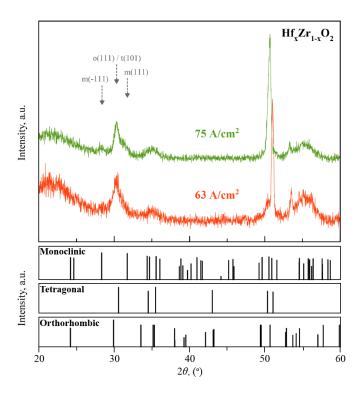

| 5.9 | GIXRD measurements showing crystallization of $Hf_xZr_{1-x}O_2$ after      |    |

|     | irradiation with IPIB                                                      | 88 |

|     |                                                                            |    |

# **List of Tables**

### **Nomenclature**

- $\varepsilon$  Dielectric permittivity

- $\kappa$  Dielectric constant

- $\mu_{FE}$  Field effect mobility

- $\psi_s$  Surface potential

- $\rho$  Electrical resistivity

- C Capacitance

- $E_c$  Coercive field

- *Ig* Gate leakage current

- *I<sub>sd</sub>* Source-drain current

- J Beam current density

- P Power

- $P_r$  Remnant polarization

- $V_g$  Gate voltage

- $V_{sd}$  Source-drain voltage

### 1. Introduction

Electronic devices have revolutionized modern society. They have had enormous impact on industry, manufacturing, information technology, healthcare, and more – pretty much every aspect our lives. We regularly carry smart phones in our pockets that would have been considered super-computers and filled a room only a few decades ago. In 1959, the invention of the metal-oxide semiconductor field effect transistor (MOSFET), and particularly later invention of the silicon-based transistor, launched a period of rapid growth in the field of electronics, with ever-increasing demands and expectations [1]. The semiconductor industry has been driven to continue delivering more and more complex and sophisticated devices by increasing the density of integrated circuits (ICs), while simultaneously decreasing their size, starting the miniaturization race. The challenges and achievements, associated with this race, can be understood by looking at two predictions that were made in 1960s-70s – Moore's Law and Dennard scaling, which were later followed by the semiconductor industry. The former predicted that the number of transistors in integrated circuits would double every two years, whereas the latter predicted even more ambitious developments. In addition to doubling the density, circuits would become 40% faster, while the power consumption would stay constant. Currently, the state-of-the-art has been able to keep pace with the Moore's Law, though it appears to be reaching fundamental limits within the current silicon paradigm. On the other hand, Dennard scaling has not been keeping pace since around 2006. In order to overcome existing obstacles and continue the scaling of transistors, while improving their performance and decreasing power consumption, novel materials and novel device architectures beyond silicon technology need to be developed. A group of experts from the semiconductors industry have reviewed possible solutions in the International Technology Roadmap for Semiconductors (ITRS), which include spin FETs, negative capacitance field effect transistors (FETs), nanoelectromechanical switches and all-spin logic devices [2]. The roadmap, among materials for the next generation electronic devices, lists carbon nanotubes,

various nanowires, III-Vs, and other materials.

The research presented here, investigates the synthesis of novel materials for next generation electronics, which includes fabrication of one- and two-dimensional semiconductors, advanced thin film high- $\kappa$  dielectrics, and thin film ferroelectrics. Novel low-dimensional semiconductors possess unique physical properties, such as ballistic conduction, high charge carrier mobility and absence of short-channel effects, making them perfectly suitable for further aggressive device miniaturization. Together with high- $\kappa$  dielectrics and ferroelectrics, it becomes possible to elucidate novel phenomena, like negative capacitance, integration of which will further contribute to future electronics size and power-supply down-scaling.

Specifically, this work focuses on three materials: single-walled carbon nanotubes, transition metal dichalcogenides, and ferroelectric  $Hf_{0.5}Zr_{0.5}O_2$ . The synthesis and engineering of these materials contribute towards a common goal – the development of negative capacitance transistors and other advanced nanoscale devices.

Carbon nanotubes. We developed process flows for the synthesis of single-walled carbon nanotube (CNT) transistors, including a novel technique for atomic layer deposition (ALD) of oxides on the inert surface of defect-free nanotubes. The latter is important since ALD typically does not form continuous layers on the nanotube surfaces that are free of nucleation sites. The proposed method utilizes  $TiO_2$ -based pretreatment of CNTs, which results in nanotubes coated with a weakly interacting, continuous layer of titania. The pretreatment strategy enables subsequent ALD of high- $\kappa$  dielectric, does not degrade the nanotube properties (that is typically expected from the surface functionalization), and increases the dielectric permittivity of the all-oxide insulator. We believe that this technique can be extended to coat CNTs with other ALD materials, such as metals, nitrides and sulfides.

Transition metal dichalcogenides. A novel transition metal dichalcogenide (TMD) synthesis method that we call "lateral conversion" was developed, which forms a structure with TMD material sandwiched between two silica layers. The technique is based on the chalcogenation of metal-oxide fims, and proceeds laterally between two inert layers forming 2D TMDs. The capping layer makes subsequent TMDs processing contamination-free, while it can also serve as a buffer layer for subsequent deposition of ALD thin films. ALD on pristine TMDs, similar to ALD on CNTs, is challenging due to the absence of nucleation sites on their surface; the developed technique overcomes this problem. The lateral conversion method utilizes standard lithographic approaches,

and enables wafer-scale synthesis of TMDs with few-layer precision, and complex lithographically defined features.

Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>. We fabricated ferroelectric thin films of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO), towards their future integration with CNTs and TMDs into negative capacitance transistors. As-synthesized HZO had an amorphous structure, so to induce the ferroelectricity, it was crystallized using two approaches: (1) conventional high-temperature annealing; and (2) a novel technique based on irradiation with intense pulsed ion beams. The former approach produced crystalline ferroelectric thin films. The latter allowed the crystallization of amorphous hafnia with an ultra-low thermal budget. We show that ion beams can controllably induce different crystallographic phases and is a promising method for producing ferroelectric HZO; ferroelectric measurements will be performed in future research.

**Dissertation contents.** Chapter 2 starts with a brief historical review of the state-of-the-art in the field of nanoscale metal-oxide-semiconductor (MOS) transistors, discussing their limitations and stating what needs to be done to overcome existing obstacles. Subsequent sections review some of the possibilities from two perspectives: changes that need to be made in device materials, and device architectures. CNTs and TMDs are discussed in the context of novel device materials, and their properties are reviewed. Next, ferroelectricity and the negative capacitance phenomena are introduced. Chapters 3 to 5 report the experimental details of three projects and the obtained results. Chapter 3 describes our fabrication of carbon nanotube transistors and a pretreatment process developed to uniformly cover the nanotube surface with high- $\kappa$  dielectric. Chapter 4 presents the lateral conversion technique used to synthesis transition metal dichalcogenides. In chapter 5, the ALD synthesis and characterization of  $Hf_{0.5}Zr_{0.5}O_2$  are discussed. Chapter 6 summarizes the obtained results and sets goals for future research.

### 2. State-of-the-art

This chapter discusses an operation principle of field effect transistors, performance requirements recognized by academia and industry, as well as future directions for transistor development.

#### 2.1. Conventional FETs and scaling theory

Metal Oxide Field Effect Transistors (MOSFETs) were first developed in 1959 at Bell Labs by Martin Atalla and Dawon Kahng [1]. The first device was based on crystalline silicon capped with thermally grown silicon oxide. Since then, the MOSFET geometry, materials, and processes to synthesize them has significantly evolved, but the operating principle, in general, remains the same. A conventional FET consists of two highly doped regions called the source and drain connected by an oppositely and moderately doped semiconductor, which is the transistor channel (see figure 2.1). A third electrode, called the gate, is formed on top or under the channel and electrically separated from it using an insulating material. When no gate voltage is applied, the transistor can be represented as two p-n junctions connected back to back, and only leakage current can flow. If a gate voltage is applied, the semiconducting channel underneath is inverted, forming an inversion channel, which connects two highly doped regions. If source-to-drain voltage V<sub>sd</sub> is applied, current starts flowing through the inversion channel and can be precisely modulated by changing the conductivity of the channel by applying an electric field from the gate terminal. For devices with such geometry, being able to fabricate transistors with perfect interfaces between components, ensuring good electrostatic coupling between gate and semiconducting channel, was a major obstacle. Silicon came to the rescue, due to the ability to grow oxide layers with perfect interfaces on the initial silicon substrate. The integration of thermally grown oxide lead to a reduction in the amount of surface states that screen applied electric field and deteriorates MOSFET performance. Moreover, Si can be controllably doped with

different chemical elements that can be use to obtain all major transistor components out of a single material.

Figure 2.1. Schematic illustration of MOSFET [3].

Increasing computation complexity required more transistors to be integrated in one device. In 1960, the first IC consisting of 16 transistors was demonstrated. Since then, both industry and scientific community have invested enormous efforts to increase the density of ICs. In 1965, Gordon Moore, at the time a R&D director at Fairchild Semiconductor, predicted that the number of components in ICs would double every two years, which is today known as "Moore's Law". Ever-growing demand from electronics required aggressive downscaling of individual transistors in order to accommodate as many devices on as small a substrate as possible. In addition to the size scaling, it was (and still is) required to further improve transistor performance, while reducing its power consumption. In 1974 Robert H. Dennard formulated a goal, according to which – with each generation, transistor density should increase twice, and ICs should become 40% faster, while the power density (and power consumption) should stay constant [4]. Since then, Moore's Law and Dennard scaling have been used to guide the industry and set the targets. Currently, Moore's law is pushing towards its limits, and Dennard scaling was abandoned around 2006. Smaller transistors, more dense architectures, difficulties with reducing operating voltage, and higher clock speeds, have resulted in heating and short-channel effects, leakage current problems, as well as increased power consumption. As a result, new materials, new device architectures and new approaches beyond conventional MOSFET technology need to be developed for further electronics miniaturization and performance improvements. Some of the ideas, proposed toward realization of this goal, will be discussed in the next section.

#### 2.2. Novel low power switches

The power required for transistor operation is mostly composed of dynamic and static power. Dynamic power, required to switch a MOSFET, is proportional to the operating voltage and has the following dependence [5]:

$$P_{dynamic} = V_{sd}^2 \times I_{av}, \tag{2.1}$$

where  $V_{sd}$  and  $I_{av}$  are source-to-drain voltage and average current, respectively. Static power or leakage power can be calculated as follows:

$$P_{static} = V_{sd} \times I_{off}, \tag{2.2}$$

where  $I_{off}$  is the off-state leakage current. Both equations constitute total power required for transistor operation and point to the conclusion that lowering operating voltage  $V_{sd}$  will lead to the reduction of total power consumption of the device.

The current flowing through the FET channel is proportional to:

$$I_{sd} \propto exp(qV_g/k_BT),$$

(2.3)

where  $k_B$  is the Boltzmann constant and T is the operation temperature [3]. The change in  $I_{sd}$ , in subthreshold region, as a function of applied gate voltage  $V_g$  is called subthreshold swing (SS) and defined as:

$$SS = \frac{\partial V_g}{\partial (log I_d)},\tag{2.4}$$

By combining equations 2.3 and 2.4, one can calculate that at room temperature the physical limit of SS is 60 mV/dec, which means that at least 60 mV needs to be applied to increase the current ten times. Such limitation also imposes a lower limit on  $V_{sd}$  and as a result the power consumption of an individual transistor.

To further investigate SS, one can extend equation 2.4 to:

$$SS = \frac{\partial V_g}{\partial (logI_d)} = \underbrace{\frac{\partial V_g}{\partial \psi_s}}_{m} \underbrace{\frac{\partial \psi_s}{\partial (logI_d)}}_{p} = \underbrace{(1 + \frac{C_s}{C_{ins}})}_{m} \underbrace{\frac{kT}{q} ln10}_{p}, \tag{2.5}$$

where  $\psi_s$  is a surface potential,  $C_s$  and  $C_{ins}$  are semiconductor and insulator

capacitances, respectively. Term m is called the body factor and represents coupling between the gate and channel, whereas n governs the conduction or injection mechanism of carriers into the channel. To lower SS value, m and n should be as small as possible. Below each case will be briefly discussed and different approaches will be studied that can be taken to achieve sub-60 mV/dec operation regime.

**Tunnel FET.** One type of device that satisfies the n < 1 requirement is tunnel FET (TFET). These devices have similar structures to conventional MOSFETs, but the conduction is based on carrier tunneling. In MOSFETs, the source-drain current is modulated by changing the conductivity of semiconducting channel, whereas in TFETs, it is based on quantum tunneling of charge carriers from valence to conduction band and vice versa. One of the early experiments demonstrated this effect in Schottky barrier carbon nanotube field effect transistors (CNFETs) [6], where band-to-band tunneling was achieved by using a dual-gate configuration. One of the gate electrodes was used to electrostatically dope a nanotube and another one was used to apply a local electric field to shift the conduction and valence bands of the nanotube. Once the conduction band bendt bellow the valence band, the band-to-band tunneling could facilitate the tunneling current, increasing  $I_{sd}$ . This approach allowed the reduction of SS to a value as low as 40 mV/dec. However, despite delivering good switching behavior, one of the main drawbacks of TFETs is low ON current, since the amount of charge carriers is limited by the tunneling effect, which is impractical for many applications.

Impact ionization MOS. Another type of transistor, which overcomes FET limitations, is an impact ionization MOS (I-MOS) device. A typical I-MOS structure consists of p+ and n+ regions (serving as source and drain respectively) that are connected by the intrinsic region. By applying a gate voltage through the gate electrode – partially overlapping intrinsic region, it is possible to control the formed inversion layer, which can reduce the effective channel length of the transistor. When high enough  $V_g$  is applied,  $V_{sd}$  starts to contribute to the electric field and increases the horizontal electric field outside the gate. At some point, the increasing vertical electrical field from  $V_g$  and the growing horizontal electric field from  $V_{sd}$  result in an avalanche breakdown, switching the device from the OFF to ON state, allowing charge carriers to surge into the channel, resulting in rapid  $I_{sd}$  growth with a very steep sub-60 mV/dec slope [7]. However, due to the close proximity of hot electrons to the oxide layer, reliability of such devices is challenging, since these electrons can be trapped, shifting the threshold voltage of

the transistor [8]. In addition, impact ionization transistors typically require high operating voltages, which negatively impact power consumption, even though the transport characteristics have a very steep slope.

Gate coupling improvement. Both TFET and I-MOS devices can improve the nterm in equation 2.5, and have their own advantages and drawbacks. However, they represent a class of devices that are different from conventional MOSFETs that are predominantly used in the semiconductor industry. Many fabrication processes have been developed and studied in detail for MOSFETs by the industry and academia. So, in this work we discuss how to improve the MOSFET performance without suggesting to replace them. As a figure of merit, the SS will be mostly used in this work, with the aim to make it as small as possible. As previously discussed, the SS can be mathematically described with two terms - m and n (see equation 2.5). For MOSFETs the thermal factor  $n = (kT/q) \times ln10$  is limited to 60 mV/dec (at room temperature), so to reduce the SS, the body factor m needs to be decreased. The body factor represents how good the electrostatic coupling between gate electrode and semiconducting channel in the FET is established. For m to be less than 1 (which will result in SS < 60 mV/dec),  $C_s/C_{ins}$  should have a negative value. This implies that either the semiconductor or insulator capacitance should have a negative value. The latter can be achieved if a ferroelectric material is integrated into the gate stack of a MOSFET, since in some circumstances ferroelectric differential capacitance can become negative. This idea was first proposed as an approach to lower SS in 2008 by Salahuddin and Data [9]. The authors suggested that this could be accomplished by integrating ferroelectric material into a FET's gate stack. A few years later, sub-60 mV/dec operation was experimentally demonstrated in numerous devices, using various ferroelectrics and channel materials (semiconductors). incorporation of a ferroelectric provides internal gate voltage amplification, and a ferroelectric capacitor serves as a step-up voltage transformer [9]. The work we present here is aimed to further develop the negative capacitance transistor approach, by investigating novel materials and their co-integration into devices. A more detailed overview of the negative capacitance phenomena is presented in chapter 2.4.1, whereas the next section will discuss what semiconductors can be used to improve the MOSFET performance.

#### 2.3. 1D and 2D nanomaterials for future electronics

The low-dimensional semiconductors that will be discussed and studied in this work are carbon nanotubes and transition metal dichalcogenides. These materials

have extraordinary mechanical, optical, thermal and chemical properties [10, 11], however, for this work we are primarily interested in utilizing their unique electronic properties in transistor applications. These alone will not significantly reduce the *SS* of FETs, but can help to overcome other problems, especially the short channel effects that start to dominate in conventional Si-based MOSFETs.

#### 2.3.1 Carbon nanotubes

Carbon nanotubes are tubular structures consisting of carbon atoms arranged in a hexagonal structure with carbon-carbon bond length of 1.421 Å. This nanomaterial was first discovered in 1952 by Radushkevich *et al.* but did not receive proper attention until 1991 after publication by Sumlo Iijima, where double-walled and multi-walled CNTs were characterized using transmission electron microscopy [12]. Two years later, single-walled nanotubes were first reported in literature and studied [13]. Ever since, CNTs have been an ongoing subject of intense research due to their exceptional physical and chemical properties. In this work we focus on single-walled nanotubes only, so **CNT will refer to single-walled CNTs**, unless otherwise specified.

Chemical structure. Elemental carbon consists of a nucleus with 6 electrons around it. Two electrons occupy the 1s orbital, forming the K shell and the remaining four electrons occupy the 2s and 2p orbitals, forming the L shell. In an excited state, each valence electron occupies 2s, 2px, 2py and 2pz orbitals. The fourth electron excitation arises from energy released during bonding. Further, during molecular interactions, the orbitals mix into hybrid orbitals to form chemical bonds, which is called hybridization. For neighboring C atoms in graphene, one s and two p orbitals mix, resulting in so-called  $sp^2$  hybridization, oriented in the x-y plane. Such in-plane hybridization of 2s,  $2p_x$  and  $2p_y$  orbitals leads to the formation of three σ-bonds, responsible for chemical bonding of C atoms. These bonds define the mechanical properties of graphene that depend on the rigidity of the bond. The remaining unhybridized out-of-plane  $2p_z$  orbital is available for  $\pi$ -bonding; it has a small binding energy and governs the electrical properties of graphene. Thus, each carbon atom provides one electron that can be easily excited by thermal energy from valence to conduction band since they overlap. As a result, graphene is a good electrical conductor or quasi-metal.

For carbon nanotubes, which can be viewed as rolled-up graphene sheets, the situation changes significantly. Bending and curvature induction change the C-C

bond length and angle;  $\pi$ -orbitals start to overlap and are no longer perpendicular to  $\sigma$ -orbitals. Depending on the angle used to roll up the graphene sheet, CNT can have different chirality and the nanotubes possess different physical and chemical properties.

Carbon nanotube lattice. Crystal lattices can be built by defining primitive unit cells and translational symmetry [14]. For graphene, the unit cell consists of two carbon atoms, however the crystallographic structure of CNTs is more complex (see figure 2.2). In the circumferential direction, the CNT lattice vector can be represented by a chiral vector:

$$C_h = na_1 + ma_2, \tag{2.6}$$

where n and m are integers, together called chirality - (n,m); whereas  $a_1$  and  $a_2$  are graphene lattice vectors. In the axial direction, the CNT lattice vector is called the translation vector and can be defined as:

$$T = t_1 a_1 + t_2 a_2, (2.7)$$

where  $t_1$  and  $t_2$  are integers. Chiral indices n and m can be used to distinguish the following types of achiral (i.e. nanotube is superimposable on its own mirror images) CNTs: (1) armchair nanotubes with (n, m = n); and (2) zigzag nanotubes with (n, m = 0). All other (n, m) CNTs are chiral. The nanotube diameter can be calculated as:

$$d_{t} = \frac{|C_{h}|}{\pi} = \frac{\sqrt{C_{h} \cdot C_{h}}}{\pi} = \frac{a\sqrt{n^{2} + nm + m^{2}}}{\pi}.$$

(2.8)

Since chiral and translation vectors are orthogonal (i.e. perpendicular to each other), their dot product is  $C_h \cdot T = 0$ , from which  $t_I$  and  $t_2$  can be derived:

$$t_1 = (2m+n)/p t_2 = -(2n+m)/p,$$

(2.9)

where p is the greatest common divisor of (2m + n) and (2n + m). The chiral angle is the angle between the chiral vector and the primitive lattice vector  $a_1$ :

$$cos\theta = \frac{C_h \cdot a_1}{|C_h||a_1|} = \frac{2n+m}{2\sqrt{n^2 + nm + m^2}}.$$

(2.10)

The number of hexagons in one unit cell is calculated using the following equation:

$$N = \frac{|C_h \times T|}{a_1 \times a_2} = \frac{2(n^2 + nm + m^2)}{p} = \frac{2|C_h|^2}{a^2 p}$$

(2.11)

Electronic properties. The electronic properties of CNTs can be derived by using the so-called zone folding scheme [15]. The first Brillouin zones of CNTs and graphene are one- and two-dimensional, respectively. The energy dispersion of graphene can be used to construct the band structure of CNTs by cutting the two-dimensional electronic dispersion relation of graphene (figure 2.2b). The number of cutting lines is equal to the number of hexagons in the unit cell of a CNT, and their length is inversely proportional to the length of the unit cell, whereas the distance between the cutting lines is inversely proportional to the diameter of CNT.

Figure 2.2. Chirality-dependent properties of carbon nanotubes. (a) Carbon nanotube chirality derivation from chiral angle, chiral and translation vectors. Reproduced from [16] with permission from the PCCP Owner Societies. (b) Zone folding scheme used to construct band-structure of CNTs from graphene. (c) Band structure and DOS obtained for two CNTs of different chirality simulated using the "CNTbands" software [17].

Graphene does not have a band gap since the valence and conduction bands of graphene touch each other at the K point in the Brillouin zone. If the cutting line, used to obtain the band structure of CNT from graphene, passes through the K point, the band gap of such a nanotube will be zero and the nanotube will be metallic. If (n,m) does not allow the cutting line to pass through the K point, a band gap will be created resulting in a semiconducting nanotube. Figure 2.2b shows cutting lines for

(12,0) and (13,0) zigzag nanotubes near graphene's K point. Since the chirality of a (12,0) tube allows one of the lines to go through the K point, the tubes possess metallic properties and the opposite can be observed for semiconducting (13,0) tubes. Band structure and density of states (DOS) for both chiralities, as well as their molecular structure are presented in figure 2.2c and d. These results were obtained using "CNTbands" simulator, available at https://nanohub.org/tools/cntbands-ext/, using  $P_z$ -orbital model [17].

**Synthesis.** The general approach to synthesize carbon nanomaterials is (a) via ablation of solid carbon or (b) pyrolysis of a carbon-containing gas such as ethylene or acetylene. As a result of such reactions, carbon atoms may arrange in a specific order to form fullerenes, graphene or carbon nanotubes. A possible undesirable byproduct is amorphous carbon. Since pyrolysis is a thermal decomposition process, typically requiring high processing temperatures at low pressures and good control over the rate that gasses are introduced into the reaction chamber. For carbon nanotubes, three main synthetic approaches based on ablation or pyrolysis exist: (1) arc discharge; (2) laser ablation; and (3) chemical vapor deposition (CVD).

Arc discharge is based on the creation of an electric arc containing carbon atoms, which can be achieved by applying high voltage between two graphite electrodes at high temperatures. Typically, the resulting product is a soot containing fullerenes, nanotubes and amorphous carbon. Next, this mixture needs to be purified to remove unwanted materials and leave CNTs only. Laser ablation utilizes a laser to vaporize graphite in a high temperature reactor. The resulting carbon vapor is carried using an inert gas (e.g. Ar) and condenses onto a water-cooled collector placed downstream. The quality and quantity of the material can be controlled by changing the laser power, reactor temperature, pressure, and catalyst nanoparticles. The latter can be used by alloying carbon targets with catalytic metals, such as Ni, Co, and their mixture.

Laser ablation and arc discharge are mostly used to synthesize large quantities of nanotubes, which can be used, for instance, to fabricate randomly oriented nanotube arrays. If additional techniques are employed, such as electrophoresis, horizontally aligned arrays can also be achieved. Both laser ablation and arc discharge require purification and very high reactor temperatures, which makes precise positioning of individual CNTs on a chip a challenging task. In this regard, chemical vapor deposition allows synthesis of nanotubes with much better control over their position on a wafer, and overall improved quality of the material.

Chemical vapor deposition. CVD is based on introducing carbon containing gas, such as CH<sub>4</sub> or C<sub>2</sub>H<sub>2</sub>, into a preheated reactor. The growth temperature can be greatly reduced by using catalyst nanoparticles in a process called vapor-liquid-solid growth. The process starts from carbon stock decomposition and dissolution into metal nanoparticles. At a specific temperature, carbon has a limited solubility in the metal. Once the metal nanoparticle is supersaturated, the carbon nanotube starts growing by one of two mechanisms. The first one is base growth, where the catalyst nanoparticle stays attached to the substrate and the CNT grows from it; the second is tip growth, during which the catalyst nanoparticle is at the growth front and precedes the precipitation of the CNT behind it. Typical CVD synthesis temperatures range between 750 and 900 °C. Growth processes with low thermal budget are typically required to minimize dopant redistribution in substrates; to eliminate diffusion of metal contacts that might exist on a substrate before the growth step, or to grow nanomaterials on flexible substrates, as well as in many other situations, where high temperature processing is undesirable or impossible.

CNT growth may take place "in air" or on-substrate, depending on how strong the interaction between the nanotube and substrate is. In the first case, tubes grow upwards and fall down either when the reaction has stopped or when the tube becomes too long and too heavy. To control the growth direction, high gas flow rates [18] or an electric field [19] can be used.

During on-substrate growth, CNTs can grow vertically – perpendicular to the substrate, or laterally along the substrate. Vertical CNT growth is often used to grow densely packed arrays of CNTs. For the types of devices discussed in this work, laterally grown CNTs are primarily considered. In this orientation, graphoepitaxy, crystallographic alignment with the substrate is possible. One of the first works that experimentally demonstrated this, used faceted nanosteps of sapphire that was cut at different angles with respect to c-plane [20] to guide nanotube growth in a given direction. Another graphoepitaxy example is CNT growth on single-crystalline quartz. This method was proven to promote highly horizontally aligned nanotube arrays. Figure 2.3a shows quartz crystal and different cuts that can be obtained from it, which are being used in numerous mechanical and electrical devices. ST-cut quartz shows particular utility, since on its surface, CNTs grow parallel to each other and along the X plane of the crystal. ST-cut is a type of rotated Y-cut with a cut angle of 42°45′. Figure 2.3d schematically shows a (5,5) single-walled nanotube on the surface of ST-cut quartz. Molecular mechanics simulations revealed that Van der Waals forces between quartz and nanotubes are responsible for the alignment, [21]

with X direction being the most energetically favorable in terms of CNT interaction with underlying Si atoms. The largest distance between silicon atoms and nanotube is in the X direction – best seen on the right image in figure 2.3d. As a result, the interaction with CNTs is minimized. Figure 2.3b shows how the interaction energy of ST-cut quartz with the nanotube depends on the orientation angle, with a global minimum at 0 degrees, i.e. along the X direction. Interestingly, nanotubes with alignment governed by Van der Waals forces, allows them to grow perpendicular to step edges and in some situations CNTs can climb over features 3 times higher than their diameter [21].

Figure 2.3. Graphoepitaxial growth of carbon nanotubes on the surface of quartz. (a) Different quartz crystal cuts available commercially [https://www.qiaj.jp/pages/frame20/page01-e.html]. (b) Nanotube orientation dependent interaction energy between CNT and ST-cut quartz. (c) SEM image of CNTs aligned along *X* direction of ST-cut quartz. (d) Schematic illustration of a (5,5) CNT on the surface of ST-cut quartz in three projections. (b-d) Adapted with permission from [21]. Copyright (2019) American Chemical Society.

In addition to the ability to grow nanotubes in predefined directions, it is important to control their location on the wafer and their chirality. The former can be achieved by patterning catalyst islands from which nanotubes will grow. The latter has yet to be achieved and is the so-called "holy grail" of CNT science. Developing a process that would enable CNT growth with predefined chirality, would immediately help nanotubes to move from academia to industry. While imperfect, many different CNT growth techniques have been developed that increase the chiral selectivity, yielding predominantly semiconducting nanotubes. For instance this was achieved by controlling catalyst type [22]; introducing methanol [23] or vapors of water [24] during the synthesis, or by selectively destroying metallic nanotubes with UV and

other radiation [25, 26]. It is also possible to perform diameter-dependent etching [27, 28], or etching of only metallic nanotubes, which can be selectively exposed with a thermocapillary polymer [29]. Another method is to burn metallic nanotubes using electrical breakdown after integration into devices by applying source-drain voltage only [30] or both source-drain and gate voltages [31].

While synthesis of single-chirality nanotubes is still challenging, it is at least possible to control the diameter distribution of CNTs. This can be done by growing them from catalyst nanoparticles of known size. Low diameter nanoparticles (below ~2 nm) define nanotube diameter and can be used to synthesize almost exclusively single-walled nanotubes. In addition to diameter control, nanoparticles density can control the density of nanotubes. Thus, growing CNTs on quartz, from lithographically defined catalyst islands with nanoparticles of known size, allows control of their growth direction, location on the wafer, and diameter distribution, respectively. This, among other issues, is still not enough to end the silicon hegemony, but sufficient for fundamental studies.

Carbon nanotube field effect transistors (CNFETs). A typical CNFET device consists of a CNT that is clamped with metallic pads from both sides, serving as source and drain electrodes. Gate electrodes can be located in close proximity to the nanotube and separated from it with dielectric. The nanotube itself plays the role of the semiconducting channel, hence the requirement of growing purely semiconducting tubes, discussed previously. CNFETs are objects of intense research due to several compelling electrical properties of CNTs: ballistic electron transport (i.e. without scattering with defects, phonons, etc.) over micrometers range [32, 33]; high field effect (>79'000 cm²/Vs) and intrinsic (>100'000 cm²/Vs) [34] mobilities at room temperature; high current densities, and absence of short-channel effect in devices as small as 9 nm [35].

Many different CNFET geometries exist and can be divided into two categories: transistors with nanotubes (1) on-substrate or (2) suspended. Devices with on-substrate nanotubes are easier to fabricate, but they typically suffer from unwanted interactions with the underlying substrate. Fixed oxide trapped charges can screen electric fields from the gate electrode, and shift threshold voltage of the transistor as a result. Another undesirable interaction is the interaction with water molecules present on the surface of the substrate. This may result in hysteretic behavior (i.e. forward and backward gate voltage sweeps have different threshold voltages), which is unacceptable for many practical FET applications, but can be

used to fabricate memory devices [36]. Higher quality oxides and/or passivation layers can be engineered to overcome the above-mentioned problems. Typically, this is realized by fabricating top-gated devices using high- $\kappa$  dielectrics such as  $HfO_2$ ,  $Al_2O_3$  and others. In addition to a higher quality interface with the nanotube, top gated devices allow switching of individual transistors in ICs, unlike common bottom gate devices.

In contrast to on-substrate devices, **nanotubes suspended in air** may offer an unaltered conduction (in terms of nanotube-substrate interaction) with hysteresis-free performance [37]. Most suspended devices are fabricated with a bottom gate, which decreases the efficiency of the electric field due to the low dielectric permittivity of air and/or relatively high distance from the nanotube. Another drawback of such a device is its fragility due to the suspension of a-few-atoms-thick nanomaterial at its "heart". However, one of the most important advantages of suspended nanotube configuration is the ability to integrate a gate electrode around the nanotube. Such configuration is typically called a **gate-all-around (GAA) geometry**, which is natural to CNTs, and provides the best electrostatic coupling between the semiconducting channel and the gate. By integrating the GAA structure with the incorporation of a thin, high-k dielectric, it should be possible to achieve ideal near-60 mV/dec SS switching behavior. Although the ideal limit has not yet been demonstrated experimentally, SS reaching a close-to-perfect 99 mV/dec operation has been shown [38].

In terms of **conduction mechanism**, two types of CNFETs exist: ohmic and Schottky barrier transistors. If the charge carriers can travel through the metal - nanotube (semiconductor) junction freely, the contact is called ohmic and the electron transport depends on the nanotube properties, i.e. the gate electrode changes the conductivity of the CNT only. If charge carriers should undergo injection into the channel through the barrier formed at the interface between semiconductor (CNT) and metallic electrode, the device is called a Schottky barrier CNFET (sb-CNFET). In this case, an electric field is needed to lower the barrier and channel resistance to turn on the transistor. With decreasing CNT channel lengths, the Schottky barrier starts to dominate and the metal-to-nanotube junction becomes more important for the conduction mechanism.

Carbon nanotubes are ambipolar in nature (i.e. can conduct both electrons and holes at positive and negative gate voltages respectively), however, in real-world devices, the contact material typically defines the polarity of sb-CNFET due to Fermi level

mismatch. If a high work function metal is used for the electrodes, such as Au or Pd, the CNFET will be p-type [39]; and if a low work function metal is used, such as Sc or Er, the CNFET will be n-type [40]. Another approach to control the polarity of the CNTFET, is to engineer an environment around it. For instance, it was shown that non-stoichiometric HfO<sub>2</sub> deposited on single-walled CNT bundles, results in n-type doping [41], despite using high-work function Pt source/drain electrodes. In addition to conductivity control, CNT passivation eliminates its interaction with the ambient environment, reducing the device-to-device variability.

#### 2.3.2 Transition metal dichalcogenides

Transition metal dichalcogenides (TMDs) are another class of materials having extraordinary physical and chemical properties and are finding more and more applications in electronic and optical devices. TMD materials have a chemical formula of ME<sub>2</sub>, where M is a transition metal, such as Mo, W, Pt or Pd; and E is one of the chalcogen atoms from group 16 of the periodic table, such as S, Se or Te. The structure and properties of TMDs are discussed in the following section.

**Structure.** TMDs may have different structures, but two of the most stable ones typically observed are octahedral 1T and trigonal prismatic 2H phases (figure 2.4a). The former has "ABC" stacking of atoms, whereas the latter has "ABA". In the 2H phase, chalcogen atoms are located in the same position in each layer of the stacked material, which is in contrast to the 1T phase, where chalcogen atoms are at an angle with regards to their "relatives" in the previous/next atomic plane.

Due to a wide variety of possible transition metal - dichalcogenide combinations, a lot of new materials have been predicted and experimentally shown, with many unique and tunable properties. Figure 2.4b shows different TMD materials, among which MoS<sub>2</sub> is one of the most studied materials with promising characteristics for electronic devices. Similar to graphene, many TMDs have two-dimensional (2D) layered structures, and have desirable quantum confined properties when isolated as few- to single-layers. Further, most of the monolayer TMDs are inherently semiconducting and no additional band gap engineering is typically required, unless specific properties need tailoring.

**Electronic properties.** Figure 2.4c shows how the band structure of  $MoS_2$  varies with the number of layers. Monolayer  $MoS_2$  is a direct band gap semiconductor with a theoretical band gap of 1.7 eV [42]. Thicker  $MoS_2$  becomes an indirect band gap semiconductor and loses some of its compelling properties, such as

strong photoluminescence, important for optoelectronic applications [43]. Another MoS<sub>2</sub> property that emerges only in monolayer material is the valley polarization phenomena, which arises due to inversion symmetry breaking and spin-orbit coupling [44]. Figure 2.4d schematically shows monolayer 2H MoS<sub>2</sub> band structure. Other TMDs also show thickness-dependent properties. For instance, the band gap of WS<sub>2</sub> changes from direct to indirect and increases with growing number of layers, while for Pt-based dichalcogenides, it is only indirect [45].

Figure 2.4. Transition metal dichalcogenides structure and electronic properties. (a) Octahedral and trigonal phases of TMDs. (b) A family of TMD materials having different physical properties. (c) Layer-dependent band structure of 2H  $MoS_2$ . (d) Schematic illustration of a monolayer 2H  $MoS_2$  band structure. Reprinted by permission from Springer Nature [46]: Journal Publisher - Nature, Nature Reviews Materials © 2017.

**Screening length.** Besides leakage current and power dissipation problems, aggressive miniaturization of electronics leads to appearance of short-channel effects. One of the ways to quantitatively evaluate them is to estimate the screening length of FETs, using the following equation:

$$\lambda = \left(\frac{\varepsilon_{body}}{\varepsilon_{ox}} \times W_{DM} \times t_{ox}\right)^{1/2}, \qquad (2.12)$$

where  $\varepsilon_{body}$  and  $\varepsilon_{ox}$  are dielectric permittivities of semiconducting channel and dielectric (oxide), respectively.  $W_{DM}$  is maximum doping dependent depletion width and  $t_{ox}$  is dielectric thickness [47]. Once the channel width  $l_c$  becomes comparable

with the screening length  $\lambda$ , charge carrier concentration starts to be more controlled by the drain electrode, rather than by the gate voltage. In general, for successful MOSFET down-scaling  $l_c$  should be ~2 times larger than  $\lambda$ . For 2D TMDs,  $W_{DM}$ becomes equal to the thickness of the material, so a low screening length can be obtained by using a-few-atoms-thick TMDs with high- $\kappa$  dielectric thin films.

**Synthesis**. The first scientific study of TMDs, particularly MoS<sub>2</sub>, dates back to 1923. In this work [48] the authors characterized the crystal structure of molybdenite using X-ray diffraction, and were able to study the arrangement of atoms in the crystal. After 40+ years of work, by 1970, about 60 TMDs were discovered, ~20 of them having layered structures [49]. However, the rapid resurgence in interest in TMDs resumed some 40 years later, after the well-known experimental demonstration of graphene. Mechanical exfoliation of graphene, TMDs, and other materials became a hot topic since the technique enabled the synthesis of high-quality monolayers on scales sufficient for fundamental studies [11, 50, 51]. Chemical exfoliation is another way of producing mono- and a few-layer TMDs [52, 53]. This is typically achieved by ultrasonication of TMD powder in an appropriate solvent. Intercalation with different atoms can be used to facilitate the process, which may require additional purification steps, otherwise intercalated material can cause phase changes, converting the semiconducting 2H phase into the metallic 1T phase [54].

The main drawback of any exfoliation approach is associated with the difficulty of scaling up the process. Precise, wafer-scale fabrication is still challenging using this method. Thus, bottom-up approaches need to be explored to make TMD fabrication compatible with very large scale integration (VLSI), which is also applicable to other nanomaterials and systems. Currently, chemical vapor deposition (CVD) is a prevalent method for large area growth of TMDs. This can be achieved by introducing transition metal and chalcogen vapors in the reactor, which can form TMDs on the substrate surface. One of the most cost-effective and widely used techniques for synthesizing TMDs involves the direct vaporization of sulfur and transition metal containing powders by heating. The vapors are carried by inert gas (e.g. Ar or N<sub>2</sub>), forming TMDs on a substrate located downstream inside the reactor, or above a boat containing the transition metal powder [55]. Metal organic chemical vapor deposition (MOCVD) has also been used to synthesize high quality wafer-scale MoS<sub>2</sub> using gas phase precursors [56]. The resulting material had a high electron mobility of 30 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature and was uniform across a 4 inch wafer.

Another related method is atomic layer deposition (ALD) [57]. In the referenced example, gas phase  $Mo(CO)_6$  and  $H_2S$  were used to produce  $MoS_2$ . Additional high-temperature annealing in  $H_2S$  atmosphere was required to improve the material's properties and stoichiometry. One of the problems with ALD of sulfides is that it requires dedicated reactor, as sulfur can cause contamination of the reactor and other materials that will be grown in the same chamber.

Yet another approach is to pre-deposit a thin film seed-layer of metal (M) [58] or metal oxide  $(MO_x)$  [59, 60], which can be later chalcogenated. This approach allows precise control over the location of the future TMD material, since the seed layer can be lithographically patterned by performing lift-off or dry/wet etching. Metals or metal oxides can be deposited using physical vapor deposition (PVD) processes, such as electron beam and thermal evaporation, or sputtering. PVD typically allows uniform thin film deposition with a thickness of 5+ nm and a precision of ~1 nm. As a result, the final material is  $5 \pm 1$  nm or thicker. After conversion, depending on the seed layer and chalcogen type, the final thickness of the TMD is even higher, resulting in a multilayer or bulk material. Thus, for monolayer and a few layer TMDs, the seed layer should be super-thin and for reproducible results, run-to-run thickness reproducibility should be sub-1 nm. Atomic layer deposition (ALD) is a perfect solution to meet the imposed seed layer thickness requirement, since it allows angstrom-level precision growth of (mostly) oxides on a wafer scale. In addition, ALD can uniformly and conformally cover high aspect ratio structures, which may enable 3D integration of TMDs into devices. ALD was used to grow WO<sub>3</sub> of different thickness ranging from 1 to 3 nm, resulting in a uniform and pinhole-free thin film on the surface of 4 inch wafer. It was shown that by changing thickness and converting the resulting oxide into sulfide, it is possible to control the number of layers in WS<sub>2</sub> and achieve monolayer material [61].

#### 2.4. Ferroelectricity and negative capacitance

Introducing the negative capacitance (NC) FET concept requires revisiting the equation 2.5 that estimates the slope of the FET transfer curve. Two conclusions were made: terms m and n, which are body factor and conduction/injection mechanisms respectively, need to be minimized to achieve steep slope performance. Since NCFETs are still FETs, n is limited to 60 mV/dec (at room temperature), so

the subthreshold swing of a FET can be rewritten as:

$$SS = \frac{\partial V_g}{\partial (log I_d)} = \underbrace{\frac{\partial V_g}{\partial \psi_s}}_{m} \times 60 \, mV/dec. \tag{2.13}$$

Thus, for FET's sub-Boltzmann operation *m* should be less than 1. A possible solution for that lies in the utilization of a material with negative capacitance in the FET gate stack. In the next section, NC phenomena, and what materials can deliver it, will be discussed and reviewed.

#### 2.4.1 Negative capacitance

A typical FET gate stack is a multilayer structure, consisting of a gate electrode and a semiconducting channel, separated with an insulator. This configuration can be treated as two capacitors connected in series, among which gate voltage  $V_g$  is divided. The ratio between the gate voltage  $V_g$  and the potential at the surface of the channel  $\psi$ , from equation 2.13 can be calculated using the following equation:

$$\frac{\partial V_g}{\partial \psi_s} = 1 + \frac{C_s}{C_{ins}}. (2.14)$$

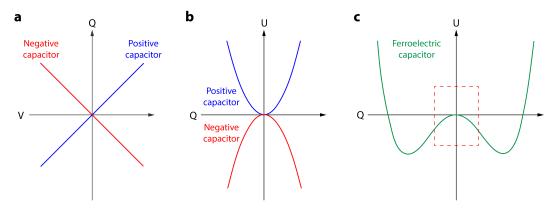

If  $C_{ins}$  will be negative, the m term in equation 2.14 will become less than 1 and it will be possible to achieve sub-60 mV/dec operation. To demonstrate the behavior of a regular (positive) or a negative capacitors, the following relationship can be used:

$$C = \frac{dQ}{dV},\tag{2.15}$$

which means that for C to be negative, the amount of charge should decrease, while increasing the applied voltage (figure 2.5a). Capacitance can also be explained from the potential energy point of view:

$$C = \left(\frac{d^2U}{dQ^2}\right)^{-1}. (2.16)$$

Figure 2.5b compares energy landscapes of a positive and negative capacitors. One

class of materials that can obtain negative capacitance values are ferroelectrics. Ferroelectric materials possess spontaneous polarization, which can be reversed by applying an electric field. Ferroelectric capacitors show a complex energy landscape, depicted in figure 2.5c, and unlike regular dielectric material, with a quadratic relation between energy and charge, ferroelectrics have two energy minima. From the Q-U relationship around Q = 0 (denoted with dashed rectangle), we can see that the curvature is oriented downwards, confirming that the ferroelectric material has a region that can have a negative capacitance (compare with the energy landscape of a negative capacitor in figure 2.5b). To demonstrate the microscopic origin of ferroelectric material polarization, figure 2.6a shows the unit cell of a ferroelectric orthorhombic phase of HfO<sub>2</sub>. Two polarization states are demonstrated, where oxygen atoms displace depending on the direction of the applied field.

Figure 2.5. Comparison between negative, positive and ferroelectric capacitors. (a) Voltage-charge characteristics. Energy landscape of (b) positive and negative, as well as (c) ferroelectric capacitors. The region under the red box in (c) signifies negative capacitance region.

Landau theory of phase transitions [62] shows that the free energy U = U(P) of a ferroelectric can be represented using the following dependence:

$$U = \alpha P^2 + \beta P^4 + \gamma P^6 - EP,$$

(2.17)

where  $\alpha$ ,  $\beta$  and  $\gamma$  are material dependent coefficients, out of which  $\beta$  and  $\gamma$  are temperature independent. Coefficient  $\alpha$  can be further written as:

$$\alpha = a_0(T - T_C), \tag{2.18}$$

where  $a_0$  is a temperature independent quantity, T is the temperature and  $T_C$  is the Curie temperature. When  $T_C > T$ ,  $\alpha$  becomes negative, which gives the negative curvature to the energy landscape of a ferroelectric material (region under red box in figure 2.5c).

The equilibrium position can be determined by finding the extremum of U:

$$\frac{dU}{dP} = 0, (2.19)$$

which, by combining with equation 2.17. will result in:

$$E = 2\alpha P + 4\beta P^3 + 6\gamma P^5. \tag{2.20}$$

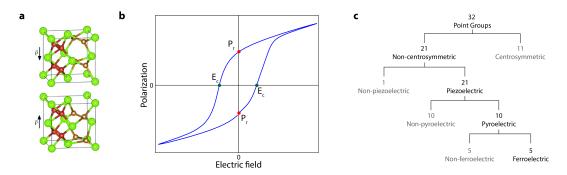

This equation represents the dependence between the external electric field and the polarizability of ferroelectric. Figure 2.6b shows the polarization-voltage characteristic of hafnium oxide, a ferroelectric that can be represented by this equation. The point where the hysteresis loop intersects with the Y-axis is the remnant polarization  $P_r$  of the ferroelectric, whereas the intersection with X-axis gives the coercive field  $E_c$ , required to switch the polarization.

Figure 2.6. Ferroelectricity and structural requirements for it. (a) Two metastable polarization states of hafnium oxide unit cell. Reproduced from the Royal Society of Chemistry [63]. (b) Typical ferroelectric hysteresis loop of doped hafnium oxide sample fabricated in this work. (c) Crystallographic families review and the ferroelectric properties.

By combining equations 2.16, 2.17 and 2.18, considering that for ferroelectrics Q = P[9], one can obtain the following equation for capacitance at P = 0:

$$C = \frac{1}{2\alpha} = \frac{1}{2a_0(T - T_C)}. (2.21)$$

For the situation when  $T_c > T$ , the capacitance becomes negative. As an example, for doped HfO<sub>2</sub> the Curie temperature was reported to be around 450 °C [64], which makes it technologically relevant for many applications.

The negative capacitance behavior was predicted by Landau in 1940 but was not experimentally measured until recently [65, 66]. The reason why it was (and still is) difficult to register this phenomenon is due to the unstable nature of negative capacitance, in which the ferroelectric self-charges and the polarization wants to be at one of the minima of the energy landscape (see figure 2.5c). The next section discusses the structural requirements for a material to have ferroelectric properties.

#### 2.4.2 Ferroelectric material structural considerations

For a material to have ferroelectric properties, it should exhibit reversable spontaneous polarization, which arises from dipoles aligning under an applied electric field. When the field is turned off, the ferroelectric material has a non-zero remnant polarization. If a high enough electric field of opposite magnitude is applied, it should be possible to switch the polarization, which will also stay when the electric field is switched off.

From a structural point of view, ferroelectric material should have a specific crystalline structure. All crystals can be divided into 32 crystallographic point group classes (figure 2.6c), 11 of which are centrosymmetric, non-polar and cannot have ferroelectric properties. The remaining 21 classes do not have center of symmetry and can be further divided into piezoelectric (20 classes) and non-piezoelectric (1 class). Piezoelectricity is the ability of a crystal to polarize electrically under applied strain. Half of the piezoelectrics do not have spontaneous polarization since their dipoles are aligned along different axes, cancelling the effect of each other. Only 10 classes, called pyroelectrics, have a unique polar axis that can contribute to spontaneous polarization and form permanent dipoles. There is no crystallographic difference between ferroelectrics and pyroelectrics. However, only ~5 out of 10 pyroelectric classes can be practical for ferroelectric application since only these classes can withstand electrical field cycling, required for polarization switching, without dielectric break-down.

Perovskite-type ferroelectrics are the most widely studied ferroelectric materials. The list includes Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub>, BaTiO<sub>3</sub>, SrTiO<sub>3</sub>, and others. The spontaneous polarization in these materials originates from the distortion of the oxygen octahedra

[63]. Perovskite materials have very high remnant polarization and dielectric constants, and are widely used in memory devices. However, perovskite-type ferroelectrics have scaling problems since they loose their ferroelectric properties once their thickness becomes less than ~70 nm [67, 68]. In this context, HfO<sub>2</sub>-based ferroelectrics are strong candidates for electronic applications, delivering high remnant polarization and low leakage current in ultra-thin films. One of the main advantages of ferroelectric hafnia is the possibility to synthesize it using ALD. ALD of doped and non-doped HfO<sub>2</sub> is a low-temperature, silicon-technology-compatible process that enables 3D integration of ferroelectric capacitors [69] and makes HfO<sub>2</sub> a unique ferroelectric material system.

#### 2.4.3 Ferroelectric HfO<sub>2</sub>

HfO<sub>2</sub>, or hafnia, is a well-known high- $\kappa$  dielectric, that has been used in the semiconductor industry for decades. It has a dielectric constant of  $\kappa = 25$  and a band gap of  $E_g = 5.8$  eV, which makes it a great choice as an insulator in FET gate stacks. Its high dielectric constant helps to maximize breakdown voltage, and its large bandgap minimizes tunneling current. Crystallized and/or doped hafnia possesses an even higher dielectric constant than amorphous hafnia, which can further support equivalent oxide thickness (EOT) scaling [70]. In 2011, a research group from Namlab (Germany) discovered ferroelectric properties in hafnia, while studying its electronic properties as a function of doping [71]. The reported thin film showed a ferroelectric hysteresis loop, with remnant polarization above  $10 \,\mu\text{C/cm}^2$ , and a coercive field of 1 MV/cm<sup>2</sup>. Yttrium doped HfO<sub>2</sub> was deposited using ALD, and by changing the number of YOx cycles, it was possible to achieve different dopant concentrations - ranging from 2.3 to 12.3 mol%. This work demonstrated synthesis of ferroelectric hafnia, with properties that could be tailored using several parameters. Today, more than 400 papers about ferroelectricity in hafnia have been published, and this number continues to grow.

Many applications are proposed for ferroelectric hafnia, which includes ferroelectric and negative capacitance field effect transistors, memory devices and others. Compared to existing ferroelectrics with perovskite type structures, hafnia is not affected by the size-effect, which was preventing continuous downscaling of thickness in conventional ferroelectric thin films [72]. Ferroelectricity has been observed in doped HfO<sub>2</sub> films as thin as 2.5 nm [73], which allows for further miniaturization of electronics and has already enabled fabrication of CMOS-compatible hafnia-based ferroelectric FETs [74], as well as

three-dimensional capacitors [69].

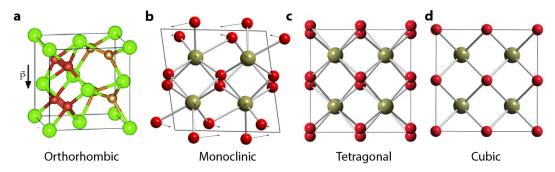

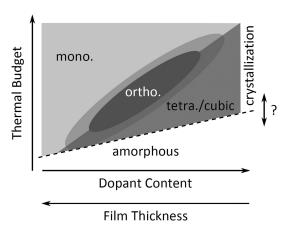

The origin of ferroelectricity in  $HfO_2$ . At standard temperature and pressure, as-obtained bulk  $HfO_2$  consists predominantly of the monoclinic phase, and if annealed goes through structural changes, transforming from monoclinic to tetragonal at ~1700 °C, and to cubic phase at ~2500 °C [75]. Figure 2.7 shows unit cells of these three phases, which have inversion symmetry, therefore polar, and do not possess ferroelectric properties.

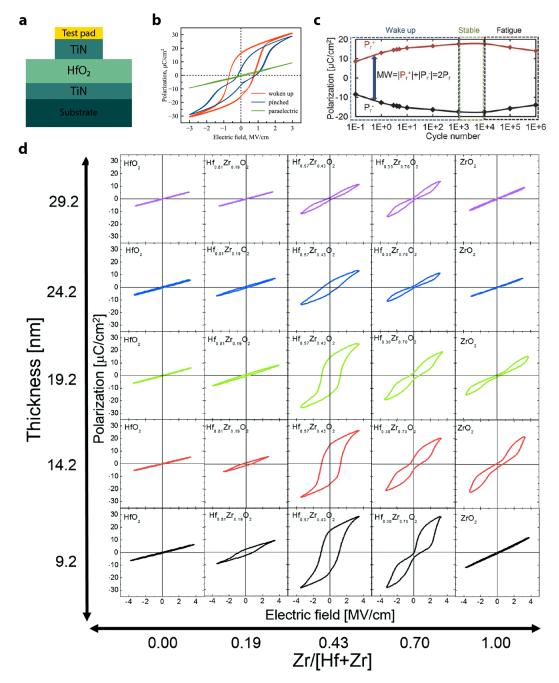

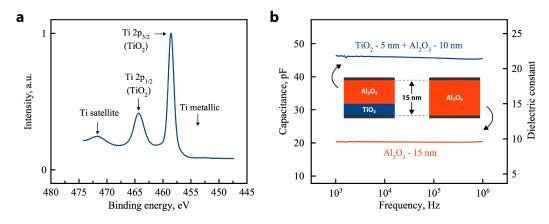

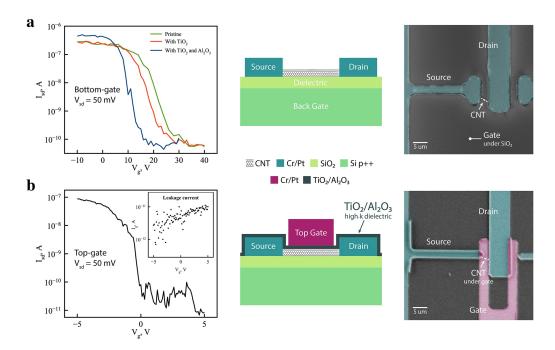

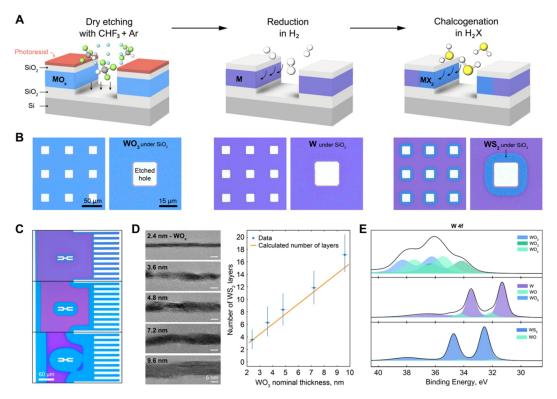

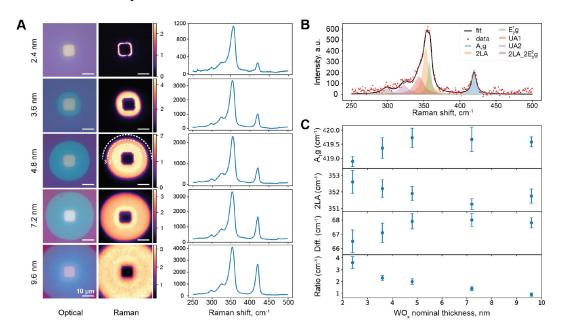

Figure 2.7. Hafnium oxide polymorphs. (a) orthorhombic, (b) monoclinic, (c) tetragonal and (d) cubic phases of HfO<sub>2</sub>. Adapted with the permission from the Royal Society of Chemistry [63] and from an open access article [76] based on CC BY license.